DS1302时钟保持芯片,让你很快读懂它

时间:2018-04-23 来源:未知

DS1302时钟保持芯片,让你很快读懂它

时间:2018-04-23 来源:未知

概述:

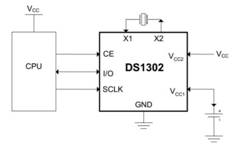

DS1302是DALLAS公司制作的涓流充电时钟芯片。芯片有实时时钟日历功能,有31*8bits静态RAM,可以通过串行接口方式和处理器(stm32,ARM等)进行通信来读写RAM,有两种传送方式,单字节传送和多字节传送。内部实时时钟日历功能逻辑电路用于提供时、分、秒、年、月、日信息(2100年之前的日期),可以自动调整闰年,闰月问题。有24小时和12小时两种格式表示。DS1302和处理器之间通过三根线连接:1、CE(低电平有效)使能线;2、I/O(Data line)数据线;3、SCLK(serial clock)串行时钟线。DS1302具有低功耗,接口简单(和处理器之间只需要三根引脚),精度高,抗干扰强等优点,工作电压(2.0V~5.5V)与TTL兼容。DS1302有年份寄存器、控制寄存器、充电寄存器、时钟突发寄存器、RAM突发寄存器、RAM存储器(31*8bits)。

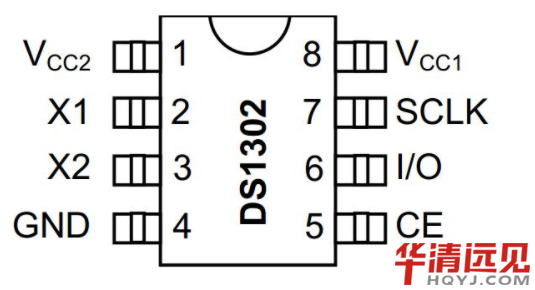

DS1302管脚排列和描述

引脚描述

X1 X2 接32.768KHz晶振引脚

GND 接地线

CE 使能引脚

I/O 数据收发引脚

SCLK 时钟引脚

Vcc1,Vcc2 供电引脚

DS1302框图如下:

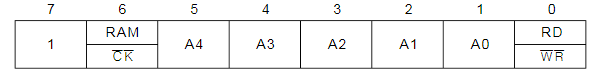

命令字:

命令字占8个比特位,如下图:

命令字节用来初始化每次数据的传输。命令字节中最高位(bit 7)必须设置为1。如果设置为0,写入会被禁止。Bit6 为0时,指定对时间\日期数据读写,如果为1时,指定对RAM数据进行读写。bit1 到 bit5指定将要被读写的寄存器是那个(芯片内部寄存器地址)。最后一个bit位(bit0)如果为0时表示写入(input),如果为1时表示读出(output)。命令字在传输的时候都是先传输低比特位(bit0)。

使能以及时钟控制:

需要传输数据时,要设置使能引脚(CE)为高电平。

使能引脚(CE)的高低电平用来提供两种功能。第一种:设置为高电平使能芯片,此时允许命令字节\地址序列去访问DS1302内部的移位寄存器。第二种:CE信号提供一个用于终止数据传输(无论是单字节传输还是多字节传输)的功能。

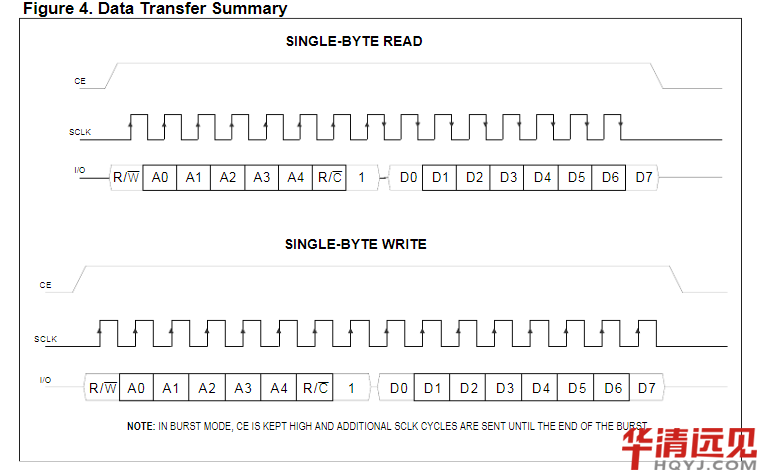

SCLK时钟线上的一个上升沿和后面紧跟着一个下降沿组成的一个方波构成了一个时钟周期。处理器向DS1302写入数据时,DS1302会在时钟周期的上升沿时采集I/O(数据线)电平状态。处理器从DS1302读取数据时,DS1302会在时钟周期的下降沿时设置I/O(数据线)电平状态。如果CE(使能信号线)输出低电平,所有的数据传输将会终止并且I/O(数据线)将会变成高阻态。下图展示了单字节的读写时序图。在刚上电时,CE(使能信号线)必须处于低电平状态(低于2.0V)。还有就是在CE(使能信号线)从低电平变为高电平期间SCLK(串行时钟信号线)必须保持低电平。

输入数据 (write)

首先传输一个写的命令字(bit0 为低电平)占用前8个时钟周期,在紧随其后的连续8个时钟周期传输一个8比特位(一个字节)的数据,每一个比特位都是在SCLK(串行时钟线)为上升沿时设置I/O(数据线)。如果不慎发生了额外的时钟周期,这些额外的时钟周期将会被忽略。数据的传输是先传送每个字节的低bit位。

输出数据(read)

首先传输一个读的命令字(bit0 为高电平)占用前8个时钟周期,在紧随其后的连续8个时钟周期传输一个8比特位(一个字节)的数据。需要注意的是,数据的第一个比特位(D0)输出是在命令字的bit7所在周期的下降沿传输。如果不慎发生了额外的时钟周期,这些额外的时钟周期将会被忽略,此时CE(使能信号线)还是高电平。同时,I/O引脚在每个时钟周期上升沿时为高阻态。数据的传输是先传送每个字节的低bit位。

突发模式:

不管是时钟/日历寄存器还是RAM寄存器都可以使用突发模式进行访问。需要把命令字的地址位(bit1 ~ bit5 )全部设置为1。设置命令字的bit6(指明操作的是时钟/日历寄存器还是RAM寄存器)。设置命令字的bit0(用于指明是读还是写)。访问时钟/日历寄存器的时候在地址9~31的位置是没有存储介质的。还有在访问RAM寄存器的时候在地址31的位置没有存储介质。在突发模式下无论是读还是写都是从0地址的bit0位开始的。

当在突发模式下写时钟\日历寄存器时,前8个寄存器必须按照顺序写入数据。但是,在突发模式下写RAM寄存器时,就没必要把所有的31字节的寄存器全部写入数据。传输的每一个字节都会被写入到RAM寄存器中,不管是否传输了31个字节。

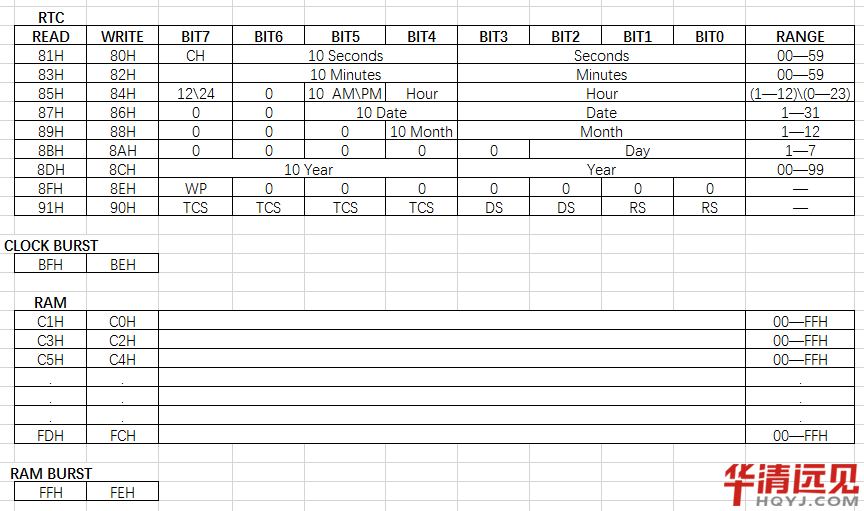

时钟/日历

读相应的寄存器可以获取时间和日期。表格3 说明了时间\日期寄存器。写响应的寄存器可以用来设置时间和日期。用BCD码的格式把时间/日期数据保存在响应的寄存器中。

在午夜凌晨的时候会递增表示星期几的寄存器。用户可以自定义表示星期天的数值是多少,但是数值必须是连续的(例如:1表示星期天,那么2就表示星期一,3就表示星期二等等)。如果输入了一些不符合逻辑的时间或者日期,会导致一些未定义的结果。

When reading or writing the time and date registers, secondary (user) buffers are used to prevent errors when the internal registers update. When reading the time and date registers, the user buffers are synchronized to the internal registers the rising edge of CE.

The countdown chain is reset whenever the seconds register is written. Write transfers occur on the falling edge of CE. To avoid rollover issues, once the countdown chain is reset, the remaining time and date registers must be written within 1 second.

DS1302可以运行在12小时制和24小时制两种模式。小时寄存器的bit7位用于决定运行在12小时制还是24小时制模式,设置为1(高电平)时就是12小时制模式。当运行在12小时的模式时,bit5用来表示是上午还是下午(AM/PM),为1(高电平)时表示PM。当运行在24小时模式时,bit5用来表示第2个10小时(20-23小时)。当切换模式的时候(修改bit7)需要重新初始化小时寄存器。

时钟停止标志:

秒寄存器的bit7位是时钟终止标志位,当bit7设置为1时,时钟振荡器将会停止振荡此时DS1302进入低功耗的待机模式,消耗电流小于100nA。当bit7设置为0时,时钟将开始工作。设备刚上电时该位没有定义。

写保护位:

控制寄存器的bit7是写保护位(WP)。前7个bit位(bit0 ~ bit6)都设置位0,如果读控制寄存器的前7个bit位(bit0 ~ bit6),读到的永远是0。在写时钟/日历或者RAM寄存器之前,控制寄存器的bit7必须是0。当写保护位(WP)是1时,会防止对任何其他寄存器的写操作。因此,如果想往设备寄存中写数据就必须先将写保护位(WP)清0。设备刚上电时该位没有定义。

涓流充电寄存器:

该寄存器决定了DS1302的充电特性。

时钟/日历突发模式:

由时钟/日历命令字来指定突发模式操作。在这种模式下,8个时钟/日历寄存器可以被连续的读出或者写入。读出或者写入的其实位置是0地址的第0个bit位。

如果设置写保护位为1时,在时钟/日历突发模式写,8个时钟/日历寄存器没有一个会发生变化(包括控制寄存器)。涓流充电器在突发模式下不可访问。

在开始读时钟的时候,当前的时间被转移到一个备用寄存器中。时间信息会从备用寄存器中读出来,在这个过程中时钟可能发生变化。这就消除了在时钟寄存器更新时需要重新读取时钟寄存器的情况。

RAM:

静态RAM大小为 31*8bits。在RAM地址空间中他们的地址是连续的。

RAM突发模式:

由RAM命令字来指定突发模式操作。在这种模式下,31个RAM寄存器可以被联系的读出或者写入。读出或者写入的其实位置是0地址的第0个bit位。

寄存器概况:

表3展示了寄存器数据格式的概况。

晶振选择:

在DS1302的X1,X2管脚上可以链接一个32,768kHz的晶振。

表3如下:

表4 如下: