STM32单片机外部晶振无效?那是因为配置不对?

时间:2021-03-21 来源:原创

STM32单片机外部晶振无效?那是因为配置不对?

时间:2021-03-21 来源:原创

1.问题的提出

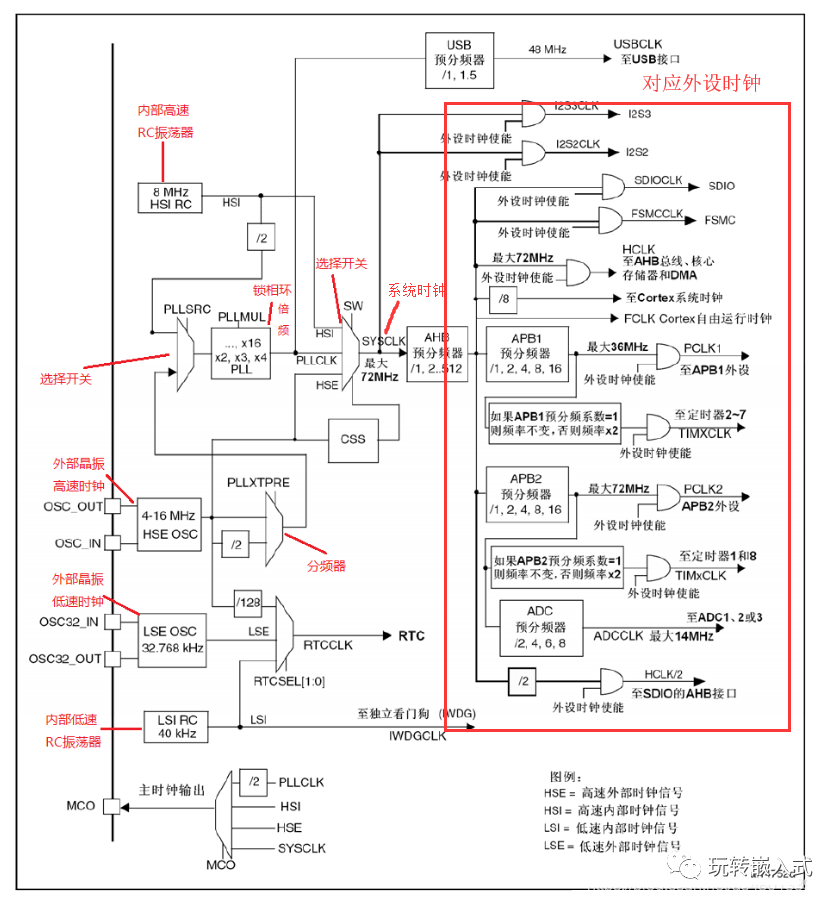

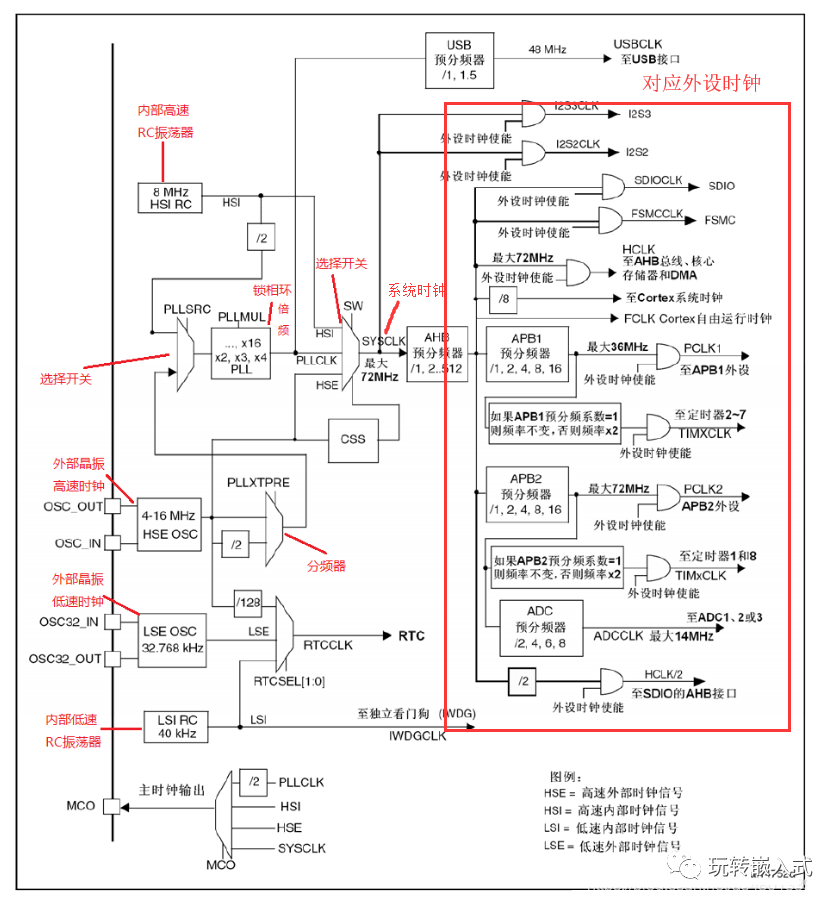

新项目用到STM32单片机,用到了500k波特率的CAN通讯,因此没有使用内部晶振,而是用到了12M的外部晶振。该项目的程序员在调试的时候发现,STM32的时钟频率不对,于是我给帮忙看了一下,找到了原因。

2.Datasheet上的答案

通过翻阅单片机的datasheet我们知道,STM32默认的外部晶振频率为8M,可输出72M的频率。于是找到了库函数的一段注释,如下:

The default value of HSE crystal is set to 8 MHz (or 25 MHz, depedning on the product used), refer to "HSE_VALUE" define in "stm32f10x.h" file.When HSE is used as system clock source, directly or through PLL and you are using different crystal you have to adapt the HSE value to your own configuration.

根据描述,将stm32f10x.h中大约在0121行将8000000修改为 12000000。

//微信公众号:玩转嵌入式,ID:micropoint8 #if !defined HSE_VALUE #ifdef STM32F10X_CL #define HSE_VALUE ((uint32_t)25000000) /*!< Value of the External oscillator in Hz */ #else #define HSE_VALUE ((uint32_t) 12000000 ) /*!< Value of the External oscillator in Hz */ #endif /* STM32F10X_CL */ #endif /* HSE_VALUE */ //微信公众号:玩转嵌入式,ID:micropoint8

3.依然无效

不过很奇怪的是,即使修改了此处的值,PLL的时钟还是不正确(PLL按9倍频配置)。

4.PLL时钟配置

顺着代码寻找原因,最后发现真正起作用的部分在 system_stm32f10x.c里的 SetSysClockTo72(void)函数(0993行,这里假设我们希望MCU工作在72MHZ)。

在1058行有这样一段代码:

#else /* PLL configuration: PLLCLK = HSE * 9 = 72 MHz */ RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE |

RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMULL6);

注释部分是函数自带的,真正起作用的部分在这里,因此把RCC_CFGR_PLLMULL9改为 RCC_CFGR_PLLMULL6。

至此,STM32可正常输出PLL时钟频率。

STM32单片机外部晶振无效?那是因为配置不对?

时间:2021-03-21 来源:原创

STM32单片机外部晶振无效?那是因为配置不对?

时间:2021-03-21 来源:原创