华清远见嵌入式普及系列活动之

高速电路设计免费技术讲座

来源:华清远见嵌入式培训中心

(蓝海微芯友情赞助ARM 2410开发板,价值2000元奖品,不容错过噢!) 本次讲座内容选取目前硬件开发工程师比较关心的热点问题,例如如何选择恰当的高速数字逻辑器件、高速数字逻辑对总线时序有什么影响、如何进行FPGA硬件小系统设计以及如何使用Cadence进行高速电路设计与仿真等,分别由华清远见三位硬件资深培训讲师担任主讲。本次活动限额200名,如有兴趣参加,请在本页面的下方提交预约信息,位置有限,先到先得。 |

|

|

|

高速电路设计免费技术讲座 |

|

|

200人 |

|

|

2007年07月14日下午1:00-5:00 |

|

|

北京理工大学7号教学楼108报告厅 |

|

|

从北理工东门进入,从主楼左侧大路直行300米即到(中心教学楼南侧) |

|

|

北京华清远见科技发展有限公司 |

|

|

软件行业协会嵌入式系统分会 |

|

|

21IC电子网 |

|

|

北京蓝海微芯科技发展有限公司 |

|

|

电话: 010-82600385/6 Email: consultant@farsight.com.cn |

|

|

||

| 时间 | 专题名称 | 主要内容 |

|

13:00~13:30 签到 |

||

|

休息交流10分钟 |

||

|

13:30 | 14:30 |

专题1 高速数字逻辑与总线缓冲器 |

1. 高速数字逻辑工艺分类 |

| 本专题主讲老师:周老师 讲师,具有10年嵌入式技术从业经验和6年嵌入式linux驱动开发经验,对于嵌入式Linux的实现和应用有深入研究,主持开发过多个大型嵌入式项目,涉及网络,通讯,控制,信息终端等各行各业,例如航天在轨数据采集系统、地震数据采集分析系统、车载MP4设备等。对系统移植有很强的经验,在X86/ARM/XSCALE/PowerPC/MIPS等各种体系结构平台上移植Linux内核;对于嵌入式Linux的实时性和CELinux的特点有深入研究。 | ||

|

休息交流10分钟 |

||

|

14:40 | 15:40 |

专题2 FPGA硬件小系统设计 |

1、FPGA小系统概念以及硬件系统的构成 |

|

休息交流10分钟 |

||

| 本专题主讲老师:姚老师 北京航空航天大学自动化专业博士学位,FPGA培训讲师,有8年的FPGA和DSP系统硬件开发经验,成功开发了卫星载超高速图像压缩系统、红外图像采集压缩和传输系统、基于MPEG4/H.264的网络监控系统、高速(1GHz)并行(4颗)DSP图像处理系统, 超大规模高速500万门FPGA验证平台(Altera StratixII EP2S180)。目前正在参与或负责多项“十五”和“十一五”预研项目以及863重点项目的硬、软件设计等工作。近4年来一直从事视频和图像处理领域的高速DSP系统硬、软件和FPGA系统的设计和开发,具有非常丰富的高速系统设计经验,精通TI公司的C6000系列高速DSP和Altera公司的全系列FPGA/CPLD。 | ||

|

15:50 | 16:50 |

专题3 Cadence高速电路设计与仿真 |

首先介绍在高速电路设计中遇到的信号完整性、时序匹配以及电磁兼容性等一系列问题。然后讲解如何用Cadence的SPB(Silicon-Package-Board)软件工具解决上述问题。主要包括:信号反射、串扰、同时开关噪声等的仿真与分析,同步时序电路的时序匹配方法,拓扑结构及其约束的确定,基于约束的布局布线,布线后分析,高速差分信号的仿真及布线等内容。 |

| 本专题主讲老师:葛老师 长期从事教学与科研工作,主要研究方向包括网络通信、视频/图像处理、数据库等。曾参与或负责过“七五”和“九五”预研项目以及863重点项目的硬、软件设计等工作。具有15年的硬件设计经验,尤其是近6年来一直从事相关领域的高速DSP系统硬、软件和FPGA开发经验数字电路设计工作,具有非常丰富的高速PCB设计经验。精通TI公司的C6000、ADI公司的TigerSHarc-201等系列高速DSP,成功开发了多个高速DSP和FPGA结合的高难度项目,尤其擅长多处理器系统的开发,熟悉多种图像/视频压缩算法,在计算机学报等刊物上发表论文20余篇。 | ||

|

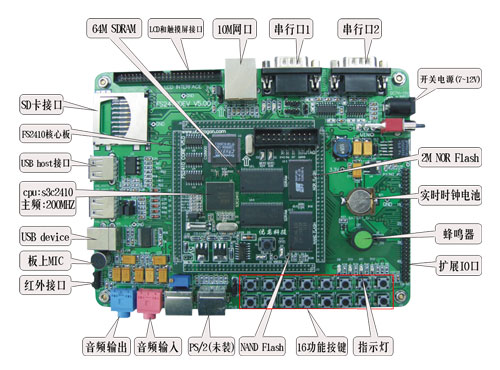

16:50~17:10 现场抽奖活动(ARM9 2410开发板,板子配置如下图所示)  |

||

|

|

|